## An Evaluation on the Accuracy of the Minimum Width Transistor Area Models in Ranking the Layout Area of FPGA Architectures

#### Farheen Fatima Khan and Andy Ye Ryerson University, Canada

#### **Motivation**

Increasing FPGA based SOC designs

> Reconfigurable fabrics benefit applications

Non-FPGA companies may use FPGA fabric

> Accurate estimation of layout area

> Early floorplanning

FPL 2016

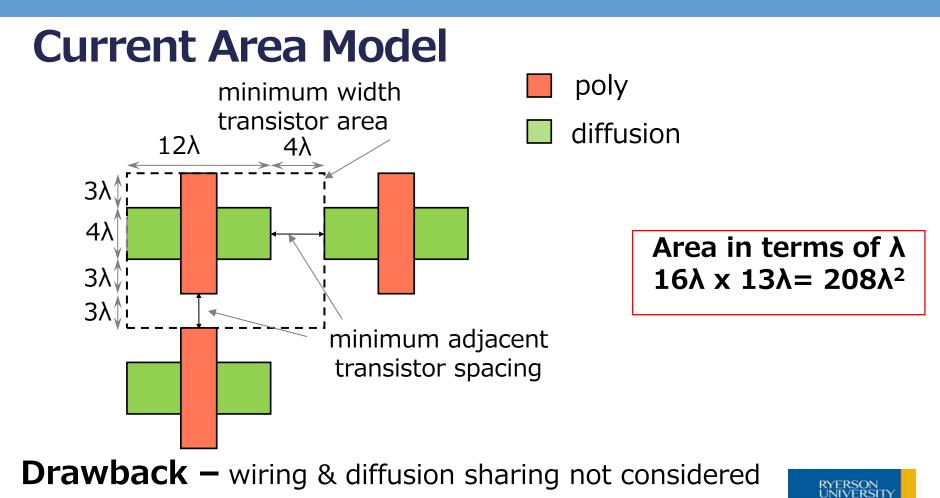

#### **VPR Area Model**

> Area(x) = 0.5 + 0.5x

1 mwt =  $208\lambda^2$

Area in terms of λ

when x=1 ; 1 mwt -> 208λ<sup>2</sup> x=2 ;1.5 mwt -> 312λ<sup>2</sup>

#### **COFFE Area Model**

>nMOS transistors

#### $1 \text{ mwt} = 208\lambda^2$

• Area(x) =  $0.447 + 0.128x + 0.391\sqrt{x}$

when x=1 ; 0.97 mwt -> 200.93λ<sup>2</sup>

>CMOS transistors

Area(x) = 0.518 + 0.127x + 0.428√x

```

when x=1 ; 1.07 mwt -> 223.18λ<sup>2</sup>

```

## **FPGA building blocks**

>nMOS based Components

Encoded and Decoded Multiplexers

CMOS based Components

- Buffers

- Full adders

#### Models accuracy at ranking different FPGA architectures ?

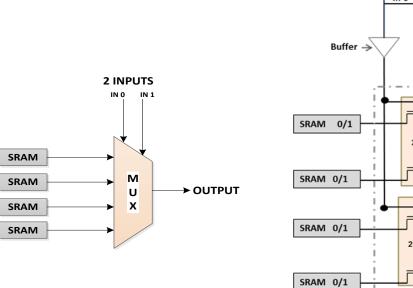

#### **Encoded Multiplexer**

- 2:1 LUT

- 4:1 Encoded Multiplexer

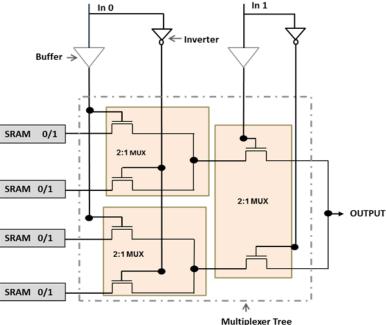

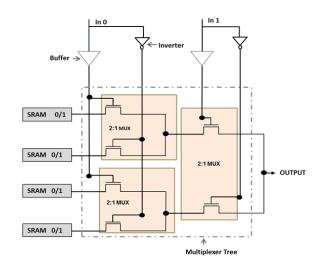

### **Decoded Multiplexer**

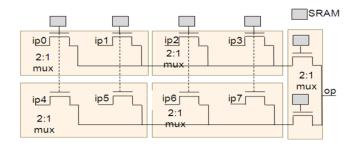

• 8:1 Decoded Multiplexer

two level multiplexer

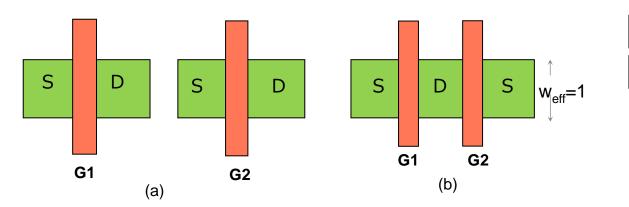

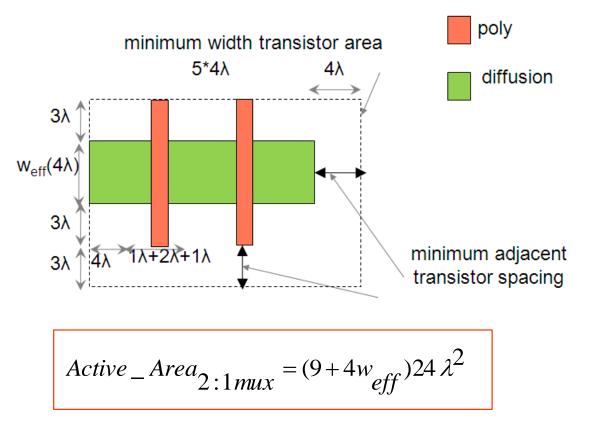

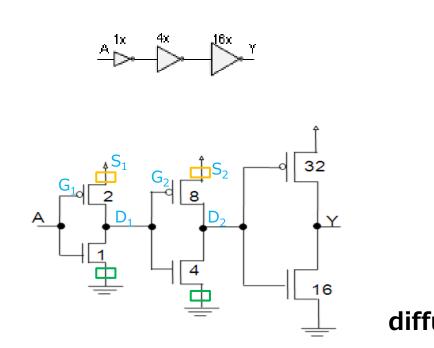

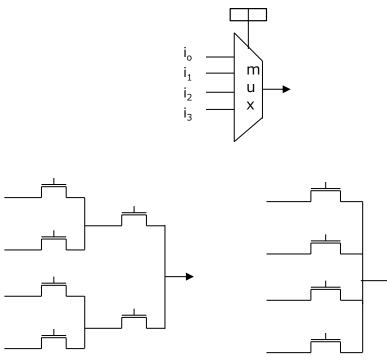

## **2:1 Multiplexer**

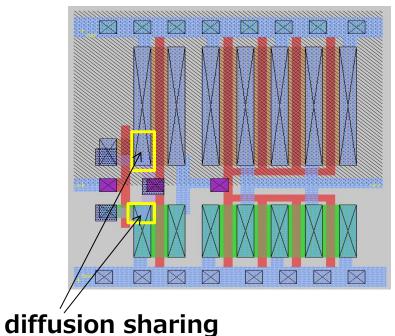

Two discrete transistors Transistors with diffusion sharing

## Effect of folding on area

| Transistor<br>size | without<br>folding       | with<br>2<br>folds | with 3<br>folds    |

|--------------------|--------------------------|--------------------|--------------------|

| 4x                 | 600λ <sup>2</sup>        | 680λ <sup>2</sup>  | 802 λ <sup>2</sup> |

| 6x                 | <b>792λ</b> <sup>2</sup> | 840λ <sup>2</sup>  | 952λ <sup>2</sup>  |

| 10x                | 1176λ²                   | 1160λ <sup>2</sup> | 1250λ <sup>2</sup> |

| 12x                | 1368λ <sup>2</sup>       | 1320λ <sup>2</sup> | 1400λ <sup>2</sup> |

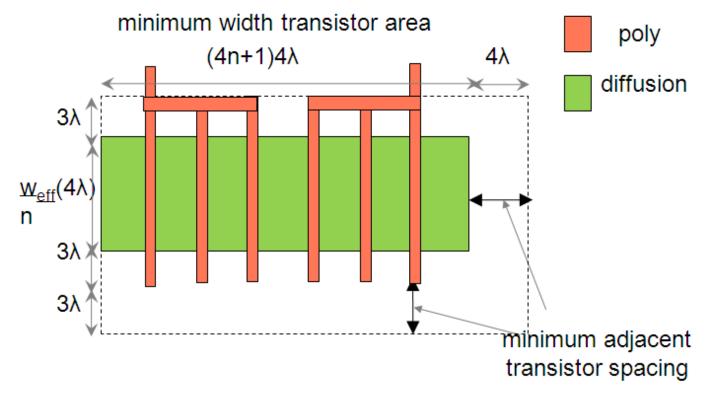

#### **Transistors with small drive strengths**

FPL 2016

# Transistors with large drive strengths

RYERSON UNIVERSITY

Active\_Area\_{2:1mux} =

$$\frac{(9n+4w_{eff})(2n+1)8}{n}\lambda^2$$

Note, if n=1, the above equation

is the same as previous equation

Active\_Area\_{2:1mux} =  $\frac{(9n+4w_{eff})(2n+1)8\lambda^2}{n\times 208\lambda^2}$  mwt

=  $\frac{(9n+4w_{eff})(2n+1)}{26n}$  mwt

=  $\frac{(9n+4w_{eff})(2n+1)}{26n}$  mwt

=  $\frac{(9n+4w_{eff})(2n+1)}{26n}$  mwt

=  $\frac{(9n+4w_{eff})(2n+1)}{26n}$  mwt

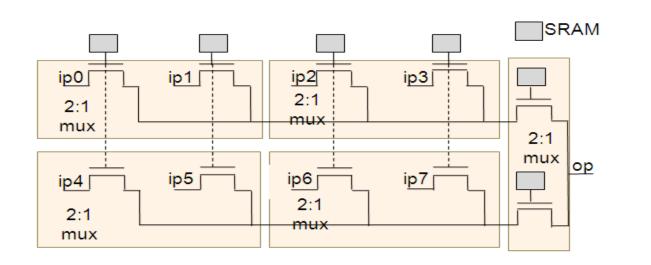

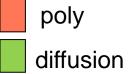

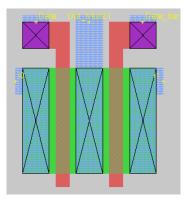

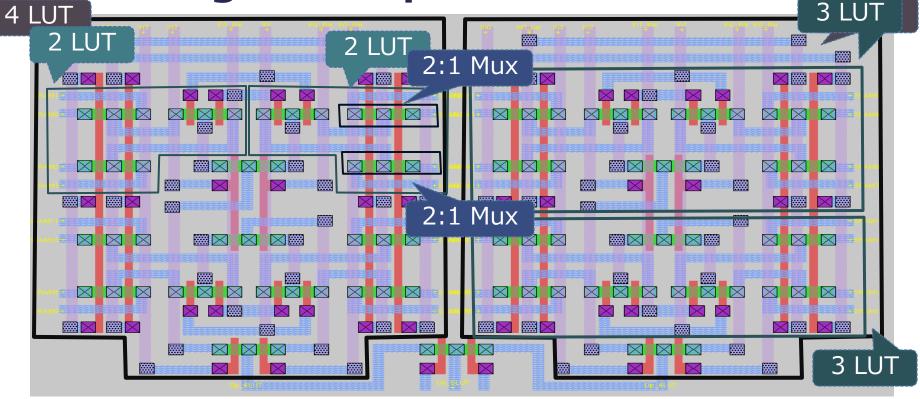

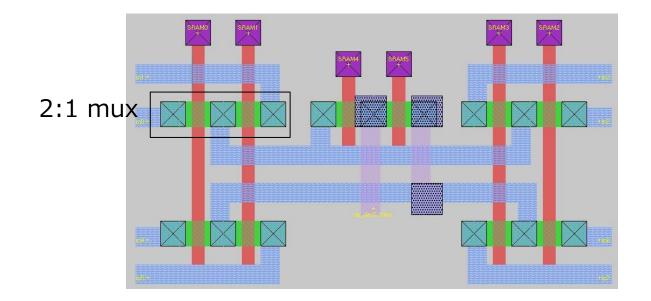

# **Layout Strategy**

## Mirroring Technique 5 LUT

#### Layout strategy for decoded multiplexer

## **Buffers - Multistage Buffer**

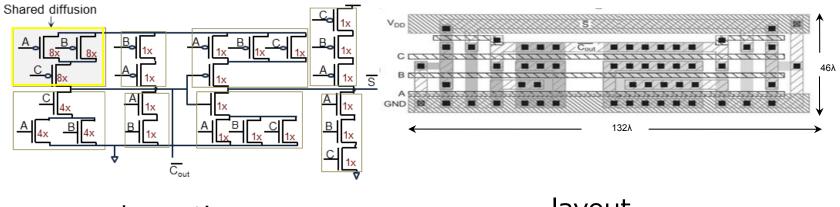

## **Full adder**

schematic

layout

#### Results

# Active area comparisonLayout area

- number of metals used

- Encoded & Decoded multiplexer

- 1x transistor size

- .change in transistor size

- CMOS based components

- buffers and full adder

#### **Active area calculation**

#### > Encoded Multiplexer

Active

$$\_Area_{k-LUT} = (2^{k} - 1)Active \_Area_{2:1mux}$$

#### k is number of inputs to LUT

#### > Decoded Multiplexer

Active\_Area<sub>z:1</sub>

$$dmux = (\frac{z}{2} + 1)Active_Area_{2:1}mux$$

# z is number of inputs to decoded multiplexer

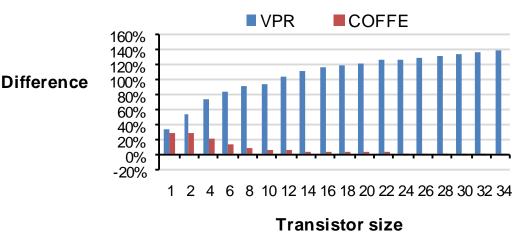

#### Active area comparison – Part I

Active Area - Encoded and Decoded Multiplexers

**VPR : overestimates** 33% to 139%

COFFE : - overestimates for 1x - 6x transistor sizes 14% to 29% - very close for large transistor sizes

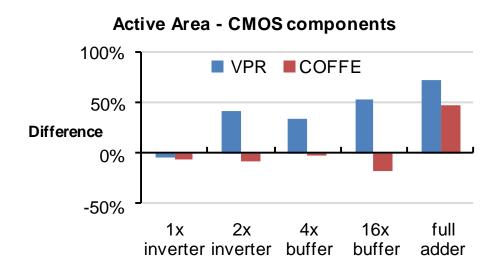

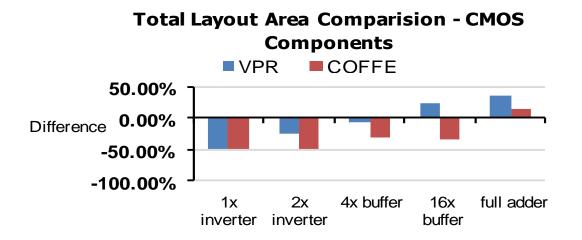

#### Part II

VPR : - underestimates 1x inverter 4%

- overestimates larger inverters, buffers & full adder 72%

COFFE : - underestimates for inverters 18%

- overestimates for full adder 46%

## **Full layout area metal layers**

**Example** : INTEL 45nm Metal Stack

| Layer | thickness(nm) | width(nm) | pitch(nm) |

|-------|---------------|-----------|-----------|

| M9    | 7 µm          | 17.5 µm   | 30.5 µm   |

| M8    | 720           | 400       | 810       |

| M7    | 504           | 280       | 560       |

| M6    | 324           | 180       | 360       |

| M5    | 252           | 140       | 280       |

| M4    | 216           | 120       | 240       |

| M3    | 144           | 80        | 160       |

| M2    | 144           | 80        | 160       |

| M1    | 144           | 80        | 160       |

### **Encoded & Decoded Multiplexer**

4:1 encoded mux

Change in transistor size

## Multiplexers – 1x transistor size

VPR

## Multiplexers – 1x transistor size

#### COFFE

## Effect of transistor size

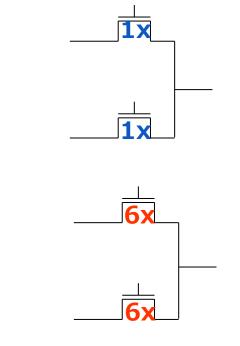

#### **VPR**

A 4 1 4 1 1

|                                                                | Metal      | Multiplexer<br>Type     | min  | max | net<br>variation |

|----------------------------------------------------------------|------------|-------------------------|------|-----|------------------|

| Total Layout Area Comparision - Transistor<br>weff=6           |            | Encoded 1x              | 56%  | 59% | 3%               |

| VPR -2metals VPR -3metals COFFE - 2metals COFFE- 3metals       | 2<br>metal | Encoded &<br>Decoded 1x | 37%  | 59% | 22%              |

| 40% ]<br>Difference 20% -                                      |            | Encoded &<br>Decoded 6x | -59% | 18% | 77%              |

|                                                                |            | Encoded 1x              | 43%  | 54% | 11%              |

| -20%40%40%                                                     | 3<br>metal | Encoded &<br>Decoded 1x | 22%  | 54% | 32%              |

| -60% <sup>J</sup><br>2- LUTor 3-LUT 4-LUT 8:1 dmux<br>4:1 dmux |            | Encoded &<br>Decoded 6x | -54% | 31% | 85%              |

.

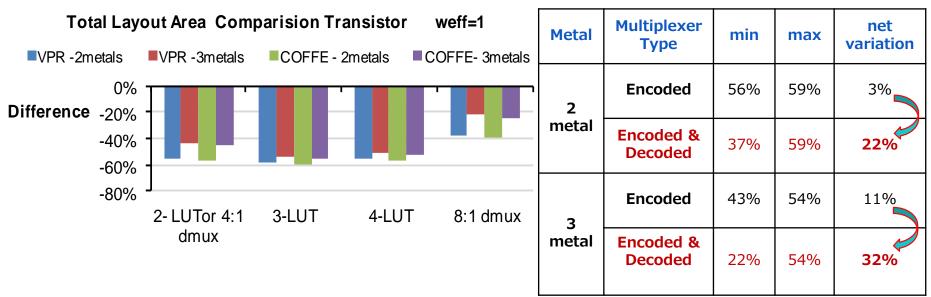

#### **Effect of transistor size** COFFE **Multiplexer** net Metal min max variation Type **Total Layout Area Comparision - Transistor** weff=6 **Encoded 1x** 57% 60% 3% VPR -2metals VPR -3metals COFFE - 2metals COFFE- 3metals Encoded & 2 39% 60% 21% Decoded 1x 40% metal 20% **Encoded &** Difference 27% 60% 33% **Decoded 6x** 0% -20% Encoded 1x 11% 45% 56% -40% **Encoded &** 3 25% 56% 31% -60% Decoded 1x metal 2-LUTor 3-LUT 4-LUT 8:1 dmux 4:1 dmux **Encoded &** 19% 56% 37%

**Decoded 6x**

#### **FPGA CMOS Components**

|       | min  | max | net<br>variation |

|-------|------|-----|------------------|

| VPR   | -50% | 34% | 84%              |

| COFFE | -51% | 13% | 64%              |

circuit topology and wiring demand differs for CMOS components

## Conclusion

#### Minimum width transistor area model

- analyzed for commonly used FPGA components

- VPR underestimates : encoded multiplexers and small size buffers overestimates : decoded multiplexers with large transistor sizes, large size buffers and full adders.

- COFFE underestimates : buffers and encoded and decoded multiplexers overestimates : full adders.

- Variation in area is due to

- different components have different circuit topologies

- > Accurate FPGA area model

- consider connectivity and grouping of adjacent transistors

- component by component area model

## Thank You.